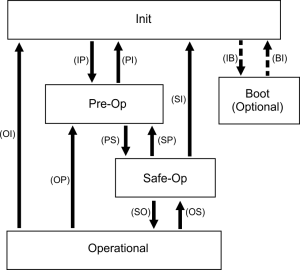

EtherCAT State Machine

The AL control, AL status and AL status code registers are responsible for communication phase run-up (also referred to as EtherCAT status change) for current status display and for any fault messages. The drive responds to every EtherCAT interface transition request made by the AL control register with the AL Status and AL Status Code registers. Any fault messages are displayed in the AL status code register.

A status change within the AL control register is polled within the AKD2G which means that an AL control event does not lead to a HW interrupt within the drive.

| Command | Address |

Bit |

ZA Drive |

ZA ECAT |

Description |

|---|---|---|---|---|---|

|

Status |

0x120 |

3 to 0 |

R/O |

W/O |

0x01: Init Request 0x02: PreOperational Request 0x03: Bootstrap Mode Request 0x04: Safe Operational Request 0x08: Operational Request |

|

Error acknowledgment |

0x120 |

4 |

R/O |

W/O |

0x00: No fault acknowledgment |

|

Reserved |

0x120 |

7 to 5 |

R/O |

W/O |

- |

|

Applic. specific |

0x120 |

15 to 8 |

R/O |

W/O |

- |

| Command | Address |

Bit |

ZA Drive |

ZA ECAT |

Description |

|---|---|---|---|---|---|

|

0x01: Init |

0x130 |

3 to 0 |

W/O |

R/O |

0x01: Init |

|

0x02: PreOperational |

|

|

|

|

|

|

0x03: Bootstrap Mode |

|

|

|

|

|

|

0x04: Safe Operational |

|

|

|

|

|

|

0x08: Operational |

|

|

|

|

|

|

Error Indication |

0x130 |

4 |

W/O |

R/O |

0x00: Acknowledgement |

|

Reserved |

0x130 |

7 to 5 |

W/O |

R/O |

- |

|

Applic. specific |

0x130 |

15 to 8 |

W/O |

R/O |

- |

| Command | Address | Bit | ZA Drive | ZA ECAT | Description |

|---|---|---|---|---|---|

| Status | 0x134 |

7 to 0 |

W/O |

R/O |

See table below |

| Status | 0x135 |

7 to 0 |

W/O |

R/O |

See table below |

| Code | Description | Current Status (Status change) |

Resulting Status |

|---|---|---|---|

| 0x0000 | No error | All | Current Status |

| 0x0011 | Invalid requested state change | I → S, I → O, P → O, O → B, S → B, P → B |

Current Status + E |

| 0x0012 | Unknown requested state | Any | I+E, P+E, S+E |

| 0x0015 | Invalid mailbox boot configuration | I → B | I + E |

| 0x0016 | Invalid mailbox configuration | I → P | I + E |

| 0x001A | Multiple sync errors, is sent when a distinction between missed SM2 event and PLL sync error cannot be made. | O, S → O | S + E |

| 0x001B | Sync manager watchdog | O, S | S + E |

| 0x001D | Invalid output configuration SM2 (Rx) | O, S, P → S | P + E |

| 0x001E | Invalid input configuration SM3 (Tx) | O, S, P → S | P + E |

| 0x0024 | Invalid input mapping (too many PDO entries) | P → S | P + E |

| 0x0025 | Invalid output mapping (too many PDO entries) | P → S | P + E |

| 0x002C | Fatal sync error (PLL was unlocked) | O | S + E |

| 0x002D | No fatal sync error (Transition SafeOp to Op took too long) | S → O | S + E |

| 0x002E | No sync error (SYNC0 did not occur) | ||

| 0x0030 | Invalid DC sync error (cycle time via register 0x9A0 is not an allowed value) | O, S → O, P → S | P + E, S + E |

| 0x0032 | DC PLL sync error (shift time too short) | O, S → O | S + E |

| 0x0034 | Too many missed SM2 events | O, S → O | S + E |

No other codes are supported.

EtherCAT Communication Phases

Individual communication transitions

|

Transition |

AL Control |

Description |

|---|---|---|

|

(IB) |

0x03 |

- |

|

(BI) |

- |

- |

|

(IP) |

0x02 |

AKD2G reads the SyncManager 0 & 1 configuration and verifies the value of the start-address and the length. The AKD2G prepares itself for handling SyncManager 0 events. |

|

(PI) |

0x01 |

- |

|

(PS) |

0x04 |

AKD2G reads the SyncManager 2 & 3 configuration and verifies the value of the start-address and the length. |

|

(SP) |

0x02 |

- |

|

(SI) |

0x01 |

- |

|

(SO) |

0x08 |

The SnycManager 2 hardware interrupt will be enabled by the drive. |

|

(OS) |

0x04 |

Deactivation of SyncManager 2 hardware interrupt. |

|

(OP) |

0x02 |

Deactivation of SyncManager 2 hardware interrupt. |

|

(OI) |

0x01 |

Deactivation of SyncManager 2 hardware interrupt. |